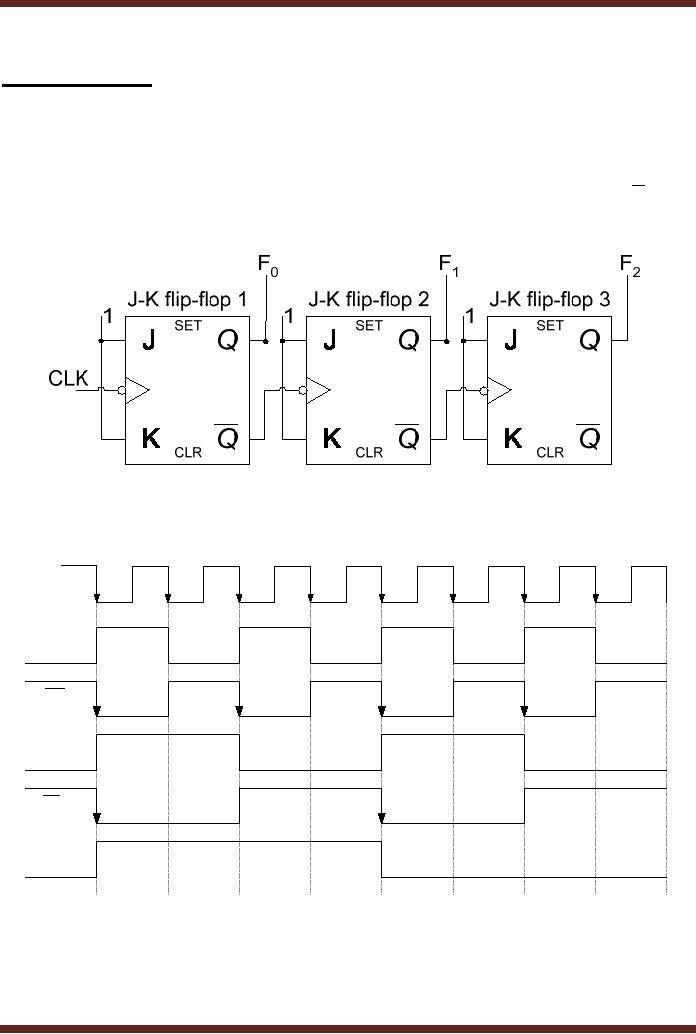

There is a 4-bit output called out which essentially provides the counter values. An active-low reset is one where the design is reset when the value of the reset pin is 0. The design contains two inputs one for the clock and another for an active-low reset. When counter is at a maximum value of 4'b1111 and gets one more count request, the counter tries to reach 5'b10000 but since it can support only 4-bits, the MSB will be discarded resulting in 0. The rollover happens when the most significant bit of the final addition gets discarded. It will keep counting as long as it is provided with a running clock and reset is held high. So, for T 1 , T 2, T 3 and T 4 we got 1, Q 1, Q 1.Q 2 and Q 1.Q 2.The 4-bit counter starts incrementing from 4'b0000 to 4'h1111 and then rolls over back to 4'b0000. Step 3: After making the excitation table the next thing to do is dig out the equation from the boolean algebra or K map for the design of the counter. Similarly, if Q 4 is 0 and Q 4‘ is 1 then T 3 become 1. When Q 4 =0 which is present state and Q 4‘=0 which is next state then T 4 become 0 State Table with excitation table Present State

So, the above table is the excitation table for T Flip Flop. So check the excitation table for T flip flop Which is: T Flip Flop Excitation Table Present state Note: To construct excitation table from state table you should know the excitation table of respective flip flop, in this case, it is T flip flop. Step 2: After that, we need to construct a state table with excitation table. So, in this, we required to make 4 bit counter so the number of flip flops required is 4.

we can find out by considering a number of bits mentioned in the question. Step 1: To design a synchronous up counter, first we need to know what number of flip flops are required. These are the following steps to design a 4 bit synchronous up counter using T flip flop:

0 kommentar(er)

0 kommentar(er)